REAL WORLD EXAMPLES

Inter-Processor Communication

In this section we will discuss about the "Interprocessor Communication". We will also implement a communication protocol for Inter-processor communication between two processors, using Shared Memory and GPIOs.

Multi-processor systems employ more than one processor to execute a given task. The multi-processor system may be as simple as a dual-processor system or as complex as to employ hundreds of processors. The multiprocessing systems generally employe one of following configurations:

(a) Different processors operate on same data, but perform different operations

(b) Different processors operate on different data (either perform same or different operations)

(c) Data processed by one processor is passed on to another processor, for further processing.

In all of the above configurations, outputs of individual processors are combined together to define the overall system output. Different processors in the system need to be in synchronization with each other in order to perform such processing tasks. Hence there is a need of communication between different processors. The communication may involve "Data Message" Transfers (where data being processed is transferred from one processor to other) or "Command Message" Transfers (where different processors may exchange command or status messages - primarily for synchronization purpose). "Data Messages" generally involve transfer of bulk data.

Schemes for Inter Processor Communication:

Interprocess can be implemented using shared memories. Since shared memory can be accessed by different processors in the system, it provides an easy way for data transfers. Dedicated interfaces across processors are another way to implement such communication. Two processors may be connected to each other using a dedicated parallel or serial interface. Some times a mix of two schemes is used - where message transfers (which involve small size data transfers) are performed over dedicated interfaces and the data transfers are performed using Shared Memories.

A simple communication protocol

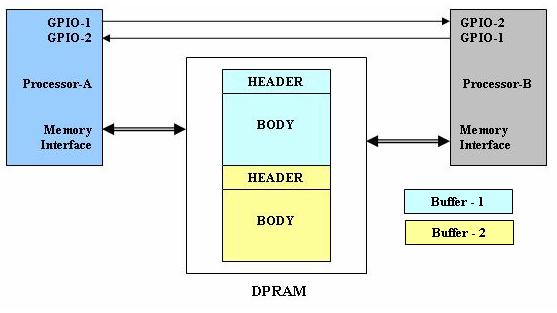

In this example, we will consider two processor which share a common memory space of 16 Kbytes. The shared memory could be implemented using DPRAM. Two GPIOs on each processor are also dedicated for this communication. One GPIO on each processor is configured as input, and is mapped to an interrupt channel. Second GPIO is configured as output.

Figure

Inter-processor communication scheme discussed under current exampleAs shown in the figure, the 16KB shared memory has been divided in to two memory buffers of 8 KBytes each. The first buffer will be used for data transfers from Processor-A to Processor-B. The second buffer will be used for data transfers in reverse direction. GPIO_1 and GPIO_2 will be used for handshake between two processors. In the given example, Processor-A is the host processor which controls the entire system. Processor-B is a co-processor which is used for performing some filtering operations on data blocks (input to the system). Processor-A also provided filter coefficients for filtering operations. These coefficients can be updated on the fly. The processor-B sends back the filter outputs back to the host processor.

Message Format:

Under current implementation, a message will contain two different fields - Header & Body. Header will be fixed length and will contain information about the message body - message type and message length. Message Body forms the actual message contents.

Message Types:

In the given example we will define three types of message. First for transferring "Data" from Processor A to Processor B. Second to transfer "Coefficients" from Processor A to Processor B. And third for transferring "Results" from "Processor-B" to "Processor-A".

Message Passing:

When a processor wants to send a message, it will copy the entrie message contents (message header and message body) in the shared memory buffer. It will then signal an interrupt to the receiver (processor to whom the message is being sent). The receiver will read the message contents and take appropriate action.

Acknowledgment:

For reliable communication, the receiver needs to send an acknowledgment back to the sender. In the given example, the receiver clears the Memory Contents (makes it 0×00) of message_type field in the message header after receiving the message. The sender must poll the contents of this memory location, to ascertain that message has been received by the receiver.

Interrupt Configuration:

The given implementation assumes "Edge Sensitive interrupt on either Edge". This scheme can be changed based on available hardware support.

Limitations:

There are few limitations to the above implementation:

(a) The maximum message size is practically limited by the size of total available shared memory. In the given example total shared memory size is 16 KBytes. We have implemented a"Duplex Communication Channel" with Maximum message size (including the message header field) of 8 KBytes. The message size can be extended to 16 KBytes - using a Simplex Communication Channel. In case of Duplex Implementation another scheme is possible - where two channels are of different sizes (e.g. 4 KBytes and 12 KBytes). This can be useful for assymetric data transfers.

(b) The given implementation supports only one message (in each direction) at a time. There is not buffer (or queue) to hold multiple messages. The scheme can be modified to have a message queue - but the maximum size of each message will decrease proportionally.

User Comments

No Posts found !Login to Post a Comment.